Podcast Flip Flops

Hoje falaremos sobre os Flip Flops, mas de uma maneira um pouco diferente... Aproveite com a gente o nosso podcast!

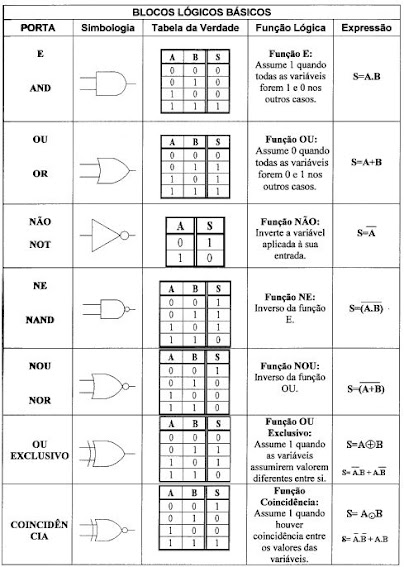

Tipos de Flip-Flops

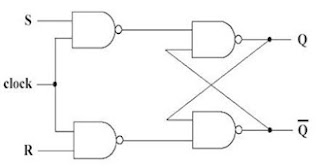

Flip-Flop tipo RS

Estrutura de Um Flip-Flop RS

Onde:

S(Set) é a entrada que posiciona a saida

Q em nivel 1. R(Reset) é a entrada que posiciona a saida Q em nivel 0.

Q representa o seinal de saida do flip-flop.

Q/ representa o complemeto do sinal de saida do flip-flop.

Flip-Flop tipo JK

O flip-flop J-K aprimora o funcionamento do flip-flop RS interpretando a

condição S = R = 1 como um comando de inversão.

Especificamente, a combinação J = 1, K = 0 é um comando para ativar (set) a

saída do flip-flo. A combinação J = 0, K = 1 é um comando para desativar

(reset) a saída do flip-flop; e a combinação J = K = 1 é um comando para inverter

o flip-flop, trocando o sinal de saída pelo seu complemento. Fazendo J = K o

flip-flop J-K se torna um flip-flop T.

Estrutura de Um Flip-Flop JK

Onde:

> é a entrada de clock

J e K são as entradas de dados

Q representa o sinal de saída do flip-flop.

Q/ representa o complemento do sinal de saída do flip-flop.

Q* é o próximo estado do Q

Flip-Flop tipo D

O flip-flop D

("data" ou dado, pois armazena o bit de entrada) possui uma entrada,

que é ligada diretamente à saída quando o clock é mudado. Independentemente do

valor atual da saída, ele irá assumir o valor 1 se D = 1 quando o clock for

mudado ou o valor 0 se D = 0 quando o clock for mudado.

Este flip-flop pode ser interpretado como uma linha de atraso primitiva ou um

hold de ordem zero, visto que a informação é colocada na saída um ciclo depois

de ela ter chegado na entrada.

Estrutura de Um Flip-Flop D

Onde:

> é a entrada de clock

D é as entradas de dados

Q representa o sinal de saída do flip-flop.

Q* é o próximo estado do Q

Flip-Flop tipo T

Se a entrada T

estiver em estado lógico alto, o flip-flop T ("toggle") muda o estado

da saída sempre que a entrada de clock sofrer uma modificação. Se a entrada T

foi baixa, o flip-flop mantém o valor anterior da saída.

Estrutura de Um Flip-Flop T

Onde:

> é a entrada de clock

T é as entrada toggle

Q representa o sinal de saída do flip-flop.

Q* é o próximo estado do Q

Referência:

http://www.mecaweb.com.br/eletronica/content/e_flip_flop

Comentários

Postar um comentário